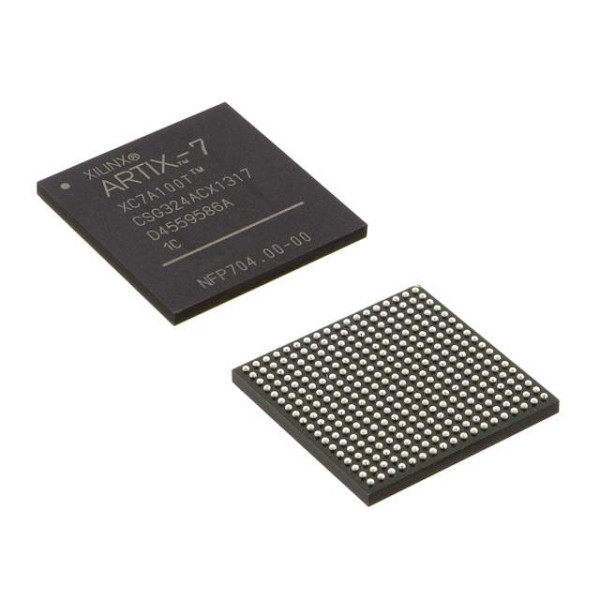

XC7A50T-2CSG324I FPGA – מערך שערים הניתן לתכנות בשטח XC7A50T-2CSG324I

♠ תיאור מוצר

| מאפיין מוצר | ערך התכונה |

| יַצרָן: | קסילינקס |

| קטגוריית מוצר: | FPGA - מערך שערים הניתן לתכנות בשטח |

| סִדרָה: | XC7A50T |

| מספר אלמנטים לוגיים: | 52160 LE |

| מספר כניסות/יציאות: | 210 קלט/פלט |

| מתח אספקה - מינימום: | 0.95 וולט |

| מתח אספקה - מקסימום: | 1.05 וולט |

| טמפרטורת הפעלה מינימלית: | - 40 מעלות צלזיוס |

| טמפרטורת הפעלה מקסימלית: | + 100 מעלות צלזיוס |

| קצב נתונים: | - |

| מספר משדרים: | - |

| סגנון הרכבה: | SMD/SMT |

| חבילה/מארז: | CSBGA-324 |

| מותג: | קסילינקס |

| זיכרון RAM מבוזר: | 600 קילו-ביט |

| זיכרון RAM משובץ - EBR: | 2700 קילו-ביט |

| רגיש לחות: | כֵּן |

| מספר בלוקי מערך לוגיקה - LABs: | מעבדה 4075 |

| מתח אספקה בהפעלה: | 1 וולט |

| סוג מוצר: | FPGA - מערך שערים הניתן לתכנות בשטח |

| כמות אריזה במפעל: | 1 |

| תת-קטגוריה: | מעגלים משולבים לוגיים ניתנים לתכנות |

| שם מסחרי: | ארטיקס |

| משקל יחידה: | 1 אונקיה |

♠ סדרת FPGA של Xilinx® 7 כוללת ארבע משפחות FPGA המטפלות במגוון המלא של דרישות המערכת, החל מיישומים בעלות נמוכה, גורם צורה קטן, רגישים לעלות ובנפח גבוה ועד לרוחב פס קישוריות, קיבולת לוגית ויכולת עיבוד אותות מתקדמים במיוחד עבור היישומים התובעניים ביותר בעלי הביצועים הגבוהים.

סדרת FPGA של Xilinx® 7 כוללת ארבע משפחות FPGA המטפלות במגוון המלא של דרישות המערכת, החל מיישומים בעלי עלות נמוכה, גודל קטן, רגישים לעלות ובנפח גבוה, ועד לרוחב פס קישוריות, קיבולת לוגית ויכולת עיבוד אותות מתקדמים במיוחד עבור היישומים התובעניים ביותר בעלי הביצועים הגבוהים. סדרת FPGA 7 כוללת:

• משפחת Spartan®-7: אופטימלית לעלות נמוכה, צריכת חשמל נמוכה וביצועי קלט/פלט גבוהים. זמין באריזה בעלת עלות נמוכה וקטן מאוד, המאפשרת שטח הדפסה קטן ביותר על המעגל המודפס.

• משפחת Artix®-7: מותאמת במיוחד ליישומים בעלי צריכת חשמל נמוכה הדורשים משדרי-מקלט טוריים ותפוקת DSP ולוגיקה גבוהה. מספקת את עלות החומרים הכוללת הנמוכה ביותר עבור יישומים בעלי תפוקה גבוהה ורגישים לעלות.

• משפחת Kintex®-7: מותאמת ליחס מחיר-ביצועים מיטבי עם שיפור כפול מהדור הקודם, המאפשרת סוג חדש של FPGAs.

• משפחת Virtex®-7: אופטימלית לביצועי מערכת וקיבולת מרביים עם שיפור כפול בביצועי המערכת. התקנים בעלי הקיבולת הגבוהה ביותר מתאפשרים על ידי טכנולוגיית חיבור סיליקון מוערם (SSI).

FPGA מסדרת 7, הבנויים על טכנולוגיית תהליך חדישה, בעלת ביצועים גבוהים, צריכת אנרגיה נמוכה (HPL), 28 ננומטר, בעלת שער מתכתי גבוה (HKMG), מאפשרים עלייה חסרת תקדים בביצועי המערכת עם רוחב פס קלט/פלט של 2.9 טרה-ביט לשנייה, קיבולת של 2 מיליון תאי לוגיקה ו-DSP של 5.3 TMAC/s, תוך צריכת חשמל נמוכה ב-50% בהשוואה להתקני דור קודם, על מנת להציע אלטרנטיבה ניתנת לתכנות מלאה ל-ASSPs ו-ASICs.

• לוגיקת FPGA מתקדמת ובעלת ביצועים גבוהים המבוססת על טכנולוגיית טבלת חיפוש (LUT) אמיתית עם 6 כניסות הניתנת להגדרה כזיכרון מבוזר.

• זיכרון RAM כפול בנפח 36 קילו-בייט עם לוגיקת FIFO מובנית לאגירת נתונים במאגר נתונים על השבב.

• טכנולוגיית SelectIO™ בעלת ביצועים גבוהים עם תמיכה בממשקי DDR3 של עד 1,866 מגה-ביט לשנייה.

• קישוריות טורית במהירות גבוהה עם משדרי-מקלט מרובי ג'יגה-ביט מובנים מ-600 מגה-ביט לשנייה ועד לקצבים מקסימליים של 6.6 ג'יגה-ביט לשנייה עד 28.05 ג'יגה-ביט לשנייה, המציעה מצב צריכת חשמל נמוכה מיוחד, המותאם לממשקי שבב לשבב.

• ממשק אנלוגי הניתן להגדרה על ידי המשתמש (XADC), המשלב שני ממירים אנלוגיים-לדיגיטליים של 12 סיביות ברזולוציית 1MSPS עם חיישני תרמיה ואספקה על השבב.

• פרוסות DSP עם מכפיל 25 x 18, אקומולטור 48-bit וקדם-מוסיף לסינון בעל ביצועים גבוהים, כולל סינון מקדמי סימטריים אופטימלי.

• אריחי ניהול שעון (CMT) רבי עוצמה, המשלבים בלוקים של לולאת נעילת פאזה (PLL) וניהול שעון במצב מעורב (MMCM) לדיוק גבוה וריצוד נמוך.

• פריסה מהירה של עיבוד משובץ עם מעבד MicroBlaze™.

• בלוק משולב עבור PCI Express® (PCIe), עבור תכנוני נקודות קצה ויציאות Root של עד x8 Gen3.

• מגוון רחב של אפשרויות תצורה, כולל תמיכה בזיכרונות Commodity, הצפנת AES של 256 סיביות עם אימות HMAC/SHA-256, וזיהוי ותיקון SEU מובנים.

• מארז שבב הפוך בעל עלות נמוכה, בעל קשרי חוטים, בעל שלמות אות גבוהה, המציע מעבר קל בין בני משפחה באותו מארז. כל המארזים זמינים באפשרות Pb ללא Pb ואריזות נבחרות זמינות באפשרות Pb.

• מתוכנן לביצועים גבוהים ולהספק הנמוך ביותר עם 28 ננומטר, HKMG, תהליך HPL, טכנולוגיית תהליך מתח ליבה של 1.0V ואפשרות למתח ליבה של 0.9V להספק נמוך עוד יותר.