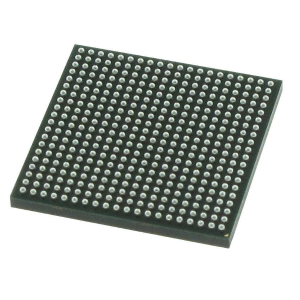

LCMXO1200C-3TN144I FPGA – מערך שערים הניתן לתכנות בשטח 1200 LUTs 113 IO 1.8 /2.5/3.3V -3 Spd I

♠ תיאור מוצר

| מאפיין מוצר | ערך התכונה |

| יַצרָן: | סָרִיג |

| קטגוריית מוצר: | FPGA - מערך שערים הניתן לתכנות בשטח |

| RoHS: | פרטים |

| סִדרָה: | LCMXO1200C |

| מספר אלמנטים לוגיים: | 1200 ליטר |

| מספר כניסות/יציאות: | 113 קלט/פלט |

| מתח אספקה - מינימום: | 1.71 וולט |

| מתח אספקה - מקסימום: | 3.465 וולט |

| טמפרטורת הפעלה מינימלית: | - 40 מעלות צלזיוס |

| טמפרטורת הפעלה מקסימלית: | + 100 מעלות צלזיוס |

| קצב נתונים: | - |

| מספר משדרים: | - |

| סגנון הרכבה: | SMD/SMT |

| חבילה/מארז: | TQFP-144 |

| אריזה: | מַגָשׁ |

| מותג: | סָרִיג |

| זיכרון RAM מבוזר: | 6.4 קילו-ביט |

| זיכרון RAM משובץ - EBR: | 9.2 קילו-ביט |

| גוֹבַה: | 1.4 מ"מ |

| מֶשֶׁך: | 20 מ"מ |

| תדירות פעולה מקסימלית: | 500 מגהרץ |

| רגיש לחות: | כֵּן |

| מספר בלוקי מערך לוגיקה - LABs: | 150 מעבדות |

| זרם אספקת חשמל הפעלה: | 21 מיליאמפר |

| מתח אספקה בהפעלה: | 1.8 וולט/2.5 וולט/3.3 וולט |

| סוג מוצר: | FPGA - מערך שערים הניתן לתכנות בשטח |

| כמות אריזה במפעל: | 60 |

| תת-קטגוריה: | מעגלים משולבים לוגיים ניתנים לתכנות |

| זיכרון כולל: | 15.6 קילו-ביט |

| רוֹחַב: | 20 מ"מ |

| משקל יחידה: | 1.319 גרם |

לא נדיף, ניתן להגדרה מחדש ללא סוף

• הפעלה מיידית – הפעלה תוך מיקרו-שניות

• שבב יחיד, אין צורך בזיכרון תצורה חיצוני

• אבטחת עיצוב מעולה, ללא זרם סיביות ליירט

• הגדרה מחדש של לוגיקה מבוססת SRAM במילישניות

• ניתן לתכנת זיכרון SRAM וזיכרון לא נדיף דרך יציאת JTAG

• תומך בתכנות רקע של זיכרון לא נדיף

מצב שינה

• מאפשר הפחתה של זרם סטטי עד פי 100

שינוי תצורה של TransFR™ (TFR)

• עדכון לוגיקה בשטח בזמן פעולת המערכת

צפיפות קלט/פלט גבוהה ללוגיקה

• 256 עד 2280 LUT4s

• 73 עד 271 כניסות/יציאות עם אפשרויות חבילה נרחבות

• נתמך נדידת צפיפות

• אריזה ללא עופרת/תואמת RoHS

זיכרון משובץ ומבוזר

• עד 27.6 קילו-ביט של זיכרון RAM משובץ sysMEM™

• זיכרון RAM מבוזר של עד 7.7 קילו-ביט

• לוגיקת בקרה ייעודית של FIFO

מאגר קלט/פלט גמיש

• מאגר sysIO™ הניתן לתכנות תומך במגוון רחב של ממשקים:

– LVCMOS 3.3/2.5/1.8/1.5/1.2

– LVTTL

– PCI

– LVDS, Bus-LVDS, LVPECL, RSDS

רכיבי PLL של sysCLOCK™

• עד שני PLL אנלוגיים לכל מכשיר

• כפל, חילוק והסטת פאזה של שעון

תמיכה ברמת המערכת

• סריקת גבולות תקן IEEE 1149.1

• מתנד מובנה

• התקנים פועלים עם ספק כוח של 3.3V, 2.5V, 1.8V או 1.2V

• תכנות בתוך המערכת תואם IEEE 1532